# Review of Network on Chip Modules, Network Concepts and Different Switching Techniques

Bhupendra Kumar Soni<sup>1</sup>, Dr. Dheeraj Jain<sup>2</sup>, Dr. Girish Parmar<sup>3</sup>

<sup>1</sup>Department of Electronics and Communication, Mewar University Chittorgarh, India <sup>2</sup>Department of Electronics and Communication, Mewar University Chittorgarh, India <sup>3</sup>Department of Electronics and Communication Engineering, Rajasthan Technical University Kota, India

Abstract — The Network-on-Chip (NoC) prototype has materialized as a innovatory methodology for incorporating a very high number of intellectual property (IP) blocks in a particular die. The feasible enactment benefit arising out of implementing NoCs is reserved by the performance restriction compulsory by the metal wire, which is the physical cognizance of communication channels.

This paper describes that NoC plays a critical role in enhancing the concert and power consumption and further development in performance can be attained by expending data compression.

*Index Terms* - Router, Network Interface, link, Network adapter, IP cores, Switching Technique.

### I. INTRODUCTION

oore's law states that the packing concentration of transistors in incorporated circuit doubles each 18 months. Today a billion numbers of transistors are packed on one single chip. The complexity and performance architecture is increasing exponentially day by day. Due to current demands, a new example in IC scheme technology called Network on Chip was projected. Using this we can enhance the performance, throughput and decrease power consumption with in a small overhead area. This NoC architecture is described as layered protocols where in packetswitching method is mostly used. Assume a system with 'n' different modules as Signal Processing, Logic units, memories etc. Communication between the modules is approved via a common system bus (Figure 1.1). Polling method is capable to exchange information between any two modules. In this, when two modules are exchanging packets, the other modules should wait till transaction gets accomplished and the medium gets released. This would rise in idle time of particular modules in the scheme. Also extra parameters, similar performance, throughput, power consumption etc. would reduce. In this situation, as number of modules increase, then it will lead to problems like; deadlock, reduction of performance and high power dissipation, etc.

Figure 1.1: Different Modules with Common Bus

### II. CONCEPTS OF NETWORK ON CHIP (NoC)

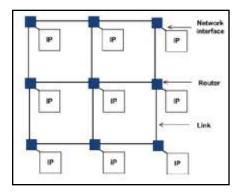

NoC consists of three components: (a) Router (b) Network Interface (c) Interconnecting links as exposed in Figure 1.2 in NoC data transmitted in form of packets. The function of routers to frontward data from source core to a target core. Network Interface is an interface between core and router. It monitors packets transmission and reception of packets from and to the core. It supports full duplex communication. Initially, it collects data from source core then packetizes, add destination address and pushes the packet at router, then it receive packet from the connected router and depacketizes, send the packet at destination core.

## Advantages of NoC

- 1. Scalability: As the volume of Interconnection links and quantity of cores increase, NoC has better scalability.

- 2. Better Performance: As parallelized traffic rises, the bandwidth of entire system leads to high bandwidth and NoC has good performance.

- 3. Reusability: In Communication infrastructure, routers and links can use within any IP core, therefore, reusability also increases.

- 4. Heterogeneous System: In NoC, IP core is isolated from communication infrastructure; it can operate at dissimilar frequency and voltage levels. This system offers Globally Asynchronous Locally synchronous design.

Figure 1.2: Network on Chip (NoC) System

# III. KEY MODULES OF NoC

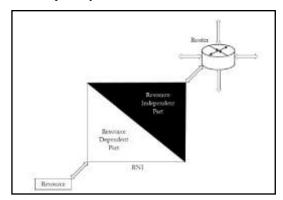

Network-on-chip is a collection of four main blocks like; Links, Router, Network interface or Network adapter, IP cores. Elementary portions of NoC are characterized in Fig. 1.4.

Figure 1.4: Basic building block of .Network-On-Chip

## Links

Link is defined as group of wires; it is used to connect two routers in the system. It may comprise single, extra logical and physical channels. NOC link form full duplexing between the routers. In this, numbers of wires are constant throughout the system according to channel. Using numbers of wires per channel live can expect the channel bit width. For implementation of link, we consider the protocol between source and destination's point of system.

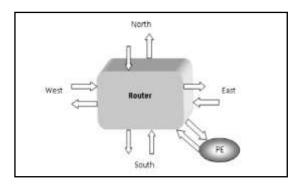

## Router

Router is important part of NOC and network system. It acts as back bone of NOC. The basic principal of router is to transfer incoming message to the target point. In any system, if router is lined to destination then data directly transfer to target. Router consists of three layers of OSI model like; physical, data link and network layer router contains routing table for routing purpose then it is called table based router. In Fig. 1.5, generic router is described which includes five ports (E, W, N, S, and L) and central cross bar matrix. Each router part contains input and output channel.

Figure 1.5: Generic Routers

# Network interface

NI plays an important role to connect resources. An IP core to a router at NOC is specified in schematic diagram of Fig.1.5. NI contains two segments:

- a) Resource dependent part

- b) Resource independent part

These parts are shown in Fig. 1.6. The main role of resource independent part is to face connect one switch to another network's switch. This part consists of some

Responsibilities like; flitization deflitization and relate encoding system. NI contains two types of layers like; session layer and transport layer.

Figure 1.6: Resource Network Interface

# IP cores

It may be general purpose controller, processor, radio frequency unit, digital signal processing unit, ADCS, PLA, Input and output controller, memory unit, etc. For IP Core, it is necessary that all resources have some technology implementation as considered for NoC. Here, the designer should use own resources reasonably than purchasing from various vendors.

# IV. SWITCHING TECHNIQUES

In this section, we will discuss different flow control techniques. This technique is responsible to create link between channels and routers. Switching methods can be classified in two categories; circuit switching and packet switching.

Circuit Switching Technique

In this switching method, firstly electrical connection is established by exchange of control signals and then the message is transmitted. Here, resources are reserved to send the message. In this arrangement link, router and network are booked in advance. After successful sending the message, source receives the acknowledgement from destination. If message size is large in this case, latency will reduce. This switching is buffer less and saving the power. If latency is low in this case, low band width is utilized. In circuit switching resources are ideal between connection setup and information transfer.

# Packet Switching

In packet switching mechanism, initially message is divided into packet and then these packets are transferred on the link. In the technique, resources are not reserved, so link utilization improves. Here, we require buffering for storing and forwarding purpose. Packet switching can be divided as follows:

- i) Store and forward (S&F) switching

- ii) Virtual cut through (VCT) switching

- iii) Wormhole switching (WS)

- *i)* Store and forward switching:

The basic principal of this switching is that initially message breakdown into a number of packets and packets are controlled by the network. In this, each resource waits up to whole message packets received by the target node. This technique will undergo from long delay at every hop which is drawback of this technique. In S&F technique, it is necessary that proper buffering should be at each node to buffer the whole packet. So, using buffering, we can improve the efficiency of S&F technique.

## ii) Virtual cut through switching

This technique is modified version of S&F switching. Here, router forwards the packet to next router according to cogent. At router, all packets will be stored first then forwarding will start at other router. Here, buffer memory is required as in S&F technique. In this VCT, latency is low. As the distance increases, probability of packet delivering at target will be declined.

# iii) Wormhole switching:

This switching technique is combination of circuit switching and VCT switching. Here, firstly by packets are allocated into minor and balanced flow control unit (flit). For flit, we follow VCT principal and as first flit receive; the route is earmarked for residual flits of packet which is defined as wormhole. This switching contains less memory compared to other two switching. In this mechanism, one flit store at a time. Latency is smaller in this so deadlock is larger. This

deadlock problem can be focused by multiplexing of some virtual ports to one physical port so traffic blocking decreases, in such a way to get dead lock free routing.

In Table 1.1, the comparison of switching methods has been shown.

Table 1.1: Summary of Different switching techniques

| Switching<br>Method     | Buffers | Remark                                                                 |

|-------------------------|---------|------------------------------------------------------------------------|

| Circuit Switching       | No      | Needs Exchange of control signal                                       |

| Store and Forward       | Yes     | packet wait before scheduled on ensuing link                           |

| Virtual Cut-<br>Through | Yes     | Head can begin next link traversal before tail arrives at current node |

| Wormhole<br>Switching   | Yes     | Head of line blocking reduces efficiency of link bandwidth             |

#### V. CONCLUSION

This paper proposes the basics concept of NoC and different parameter related to it. Different switching mechanism and comparative summary for mechanism is discussed. In switching technique buffers play very important role to improve the system performance. Wormhole switching contains less memory compared to other two switching. In this mechanism, one flit store at a time. Latency is smaller in this and deadlock free routing.

#### REFERENCES

- Amin Mehranzadeh and Mehdi Hoodgar, "Fault aware routing algorithm based on XY algorithm for network on chip", Global Journal of Computer Science and Technology, Vol. 11, No. 17, pp.58-62, 2011.

- [2]. Rajesh Nema and Parvinder Singh Khanna, "Implementation of two phase X-Y routing in NOC router", *International Journal of Engineering Sciences & Management*, Vol. 2 pp. 276-281, 2012.

- [3]. Shubhangi D Chawade and Mahendraa Gaikwad, "Review of XY routing algorithm for network on chip architecture", "International Journal of Internet Computing" Vol. 1, No. 4, pp. 48-52, 2012.

- [4]. Shubhangi D Chawade, Mahendra A Gaikwad, Rajendra M Patrikar, "Design XY routing algorithm for NoC architecture", www.ijrdonline.com.

- [5]. Dinesh Lekariya and Dr. M.A. Gaikwad, "Performance analysis of minimum hop source routing algorithm for two dimensional torus topology NOC architecture under CBR traffic", IOSR *Journal of Electronics and Communication Engineering (IOSR-JECE)* Vol.7, No. 2,PP 05-12, 2013.

- [6]. Parag Parandkar, Jayesh Kumar Dalal and Sumant Katiyal, "Performance comparison of XY, OE and DYAD routing algorithm by load variation analysis of 2-dimensional mesh topology based network-on-chip", BIJIT - BVICAM's International Journal of Information Technology, Vol. 4, No.1, pp.391-396, 2012.

- [7]. Sudhanshu Choudhary and Shafi Qureshi, "Performance evaluation of mesh-based NoCs: implementation of a new architecture and routing algorithm", *International Journal of Automation and Computing*, Vol. 6, No.2, pp. 403-413, 2012.

- [8]. Naveen Choudhary, M. S. Gaurand V. Laxmi, "Escape path based irregular network-on-chip simulation framework", Evolution in Networks and Computer Communications, A Special Issue from IJCA - www.ijcaonline.org.